-

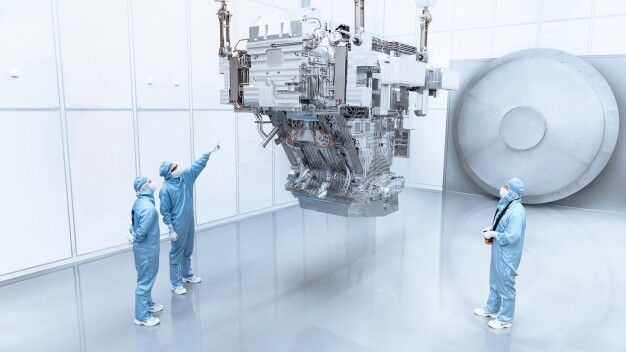

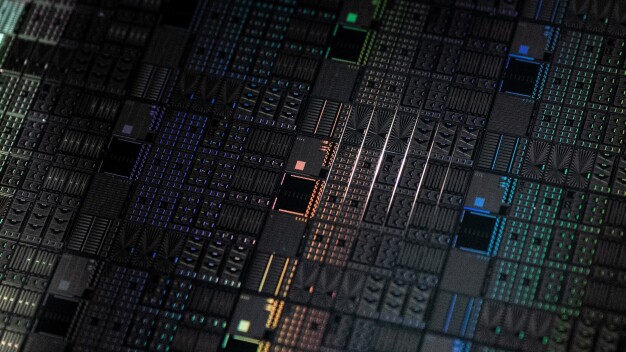

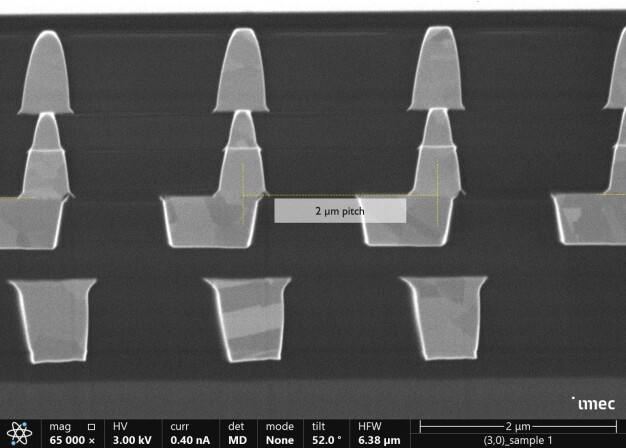

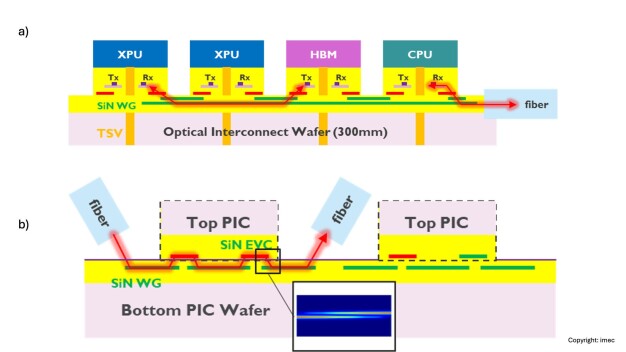

- Electronics (wafers, semiconductors, microchips,...)

Consortium to facilitate access to design infrastructure, training, and capital for European fabless semiconductor startups, small and medium enterprises and research organizations.

Imec coordinates EU Chips Design Platform

A consortium of 12 European partners, coordinated by imec, has been selected in the framework of the European Chips Act to develop the EU Chips Design Platform. Funded by Chips JU, the platform will facilitate access to advanced semiconductor design infrastructure, training, and capital for fabless…